PACS: 85.30.De

# New nonlinear model to determine $C_{gs}$ and $C_{gd}$ capacities of GaAs MESFET

## N. Merabtine<sup>1</sup>, S. Amourache<sup>2</sup>, Y. Saidi<sup>2</sup>, M. Zaabat<sup>3</sup>, Ch. Kenzai<sup>2</sup>

<sup>1</sup>Laboratoire Eléctromagnétisme et Télécommunication, Faculté des Sciences de l'Ingénieur Université Mentouri Constantine

<sup>2</sup>Laboratoire des couches minces, Faculté des sciences Université MENTOURI Constantine ALGERIA

<sup>3</sup>Departement de physique, Institut des science Exactes Centre Universitaire d'Oum el Bouaghi 04000 OUM EL BOUAGHI, ALGERIA

e-mail: zaabat@hotmail.com

**Abstract.** New nonlinear model for simulating physical and geometrical parameters to determine the junctions capacities of "the Gallium Arsenide Metal Semiconductor Field Effect Transistor" GaAs MESFET are represented in this paper. Non linear variations of the bias and gate-source and gate-drain capacities have been found. A simulated values show excellent agreement with experimental results.

Keywords: modelling, capacities, MESFET GaAs.

Paper received 19.03.03; accepted for publication 17.06.03.

# 1. Introduction

We propose a calculus model of the gate-source and gate-drain capacities of the MESFET GaAs, noted respectively  $C_{gs}$  and  $C_{gd}$ , based on the distribution configuration of the fixed charge in the depletion region, this one is subdivided for an internal and external parts. The first one is located directly under the gate of the transistor and is the origin of the intrinsic capacities. The second one is presented by the extensions of the internal zone in both source and drain directions, and it is the origin of the extrinsic or parasitic capacities.

The simulation of non linear circuit using GaAs MESFET devices utilising our model, give the variation of the charge for drain and gate region with polarisation and to physical and geometrical parameters of the component, and reveals also the C(V) characteristics in the linear and saturated regimes of the transistor.

# 2. Determination of the charge of the depletion region

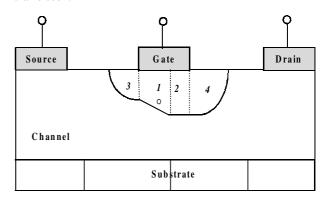

The fixed charge of the depletion region of the component are distributed in four regions (Fig. 1):

1° / the not saturated region of the channel under the gate;

$2^{\circ}$  / the saturated region of the channel under the gate which exists only in saturation mode;  $3^{\circ}$  and  $4^{\circ}$  / are respectively the extensions of the depletion region in both source and drain directions.

To determine the gate-source and gate-drain capacities, first we must determine the expressions of the charge in these regions, in the two modes of polarisation of the transistor.

Fig. 1. Repartition of the fixed charge on the depletion region.

# 2.1. Linear regime

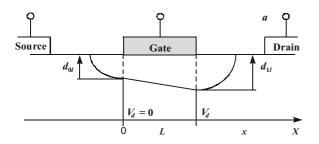

When drain voltage is weak, the gradual channel approximation is utilised in all the internal part of the depletion region, to determine the effect edge around gate contact in this region (Fig. 2a) [2]. In this case, the charge in this zone can be calculated by the following expression:

$$Q_{gl} = qN_d Z \frac{L}{2} \{ d_{0l} + d_{1l} \}$$

(1)

Where q – the electron charge,  $N_d$  – the electrons density, L and Z are respectively the length and the width of the channel,  $d_{0l}$ ,  $d_{1l}$  are respectively the widths of the depopulated zone in both source and drain directions (Fig. 2a), expressed as follows:

$$d_{0l} = a \sqrt{\frac{V_{bi} + V_g}{V_p}} \tag{1a}$$

$$d_{1l} = a \sqrt{\frac{V_{bi} + V_d + V_g}{V_p}} \tag{1b}$$

With a – the thickness of the channel,  $V_{bi}$  – the built-in voltage of GaAs,  $V_p$  – the pinch-off voltage,  $V_g$  – the gate voltage and  $V_d$  – the drain voltage. In the other hand, the edges of the depopulated extensions are considered as circle portions (Fig. 2a) in both source and drain directions [3–6]. Thus, the charges stored in these two zones, noted  $Q_{sl}$  and  $Q_{dl}$  are calculated as follows:

$$Q_{sl} = qN_d Z \frac{\pi}{2} \frac{d_{0l}^2}{2} \tag{2}$$

Fig. 2. Configuration of the depletion region. a – linear regime; b – saturated regime.

$$Q_{dl} = qN_d Z \frac{\pi}{2} \frac{d_{1l}^2}{2}$$

(3)

From where the total charge  $Q_{gpl}$ , due to the depopulated extensions is:

$$Q_{gpl} = Q_{sl} + Q_{dl} \tag{4}$$

$$Q_{gpl} = qN_d Z \frac{\pi}{2} \left\{ \frac{d_{0l}^2 + d_{1l}^2}{2} \right\}$$

(5)

The total charge  $Q_l$  of the gate in the linear mode is then equal to the sum of  $Q_{gl}$  and  $Q_{gpl}$  charges:

$$Q_l = Q_{gl} + Q_{gpl} \tag{6}$$

$$d_{1l} = a\sqrt{\frac{V_{bi} + V_d + V_g}{V_p}} \tag{7}$$

#### 2.2. Saturation mode

The transistor configuration is represented on Fig. 2b where it is seen clearly that the intrinsic zone is subdivided into two parts. In the first part, the gradual channel approximation remains always valid, whereas in the second part, the effect edge is constant, for an invariant value of the drain voltage [6]. Under these conditions, the  $Q_{g0s}$  and  $Q_{g1s}$  charges, which are, stored in these two parts are expressed as follows:

$$Q_{g0s} = qN_d Z \frac{(L - Ls)}{2} \{ d_{0s} + d_{1s} \}$$

(8)

$$d_{0s} = a \sqrt{\frac{V_{bi} + V_g}{V_p}} \tag{8a}$$

$$d_{1s} = a\sqrt{\frac{V_{bi} + V_d + V_g}{V_p}} \tag{8b}$$

$$Q_{g1s} = qN_d ZL_s d_{1s} (9)$$

With  $L_s$  – the length of the constant part. Its expression is given by the following relation [2,8]:

$$L_s(V_d, V_g) = \frac{2a}{\pi} \sinh^{-1} \left\{ \frac{\pi K_d}{2aE_s} \left( V_d - V_c \right) \right\}$$

(10)

$V_c$  is the voltage drop between the source and the onset of the saturation region, i.e. with  $X = L - L_s$ . It's expression is as follows[2]:

$$V_{c}(V_{g}) = \frac{(V_{g} - V_{p})E_{s}L}{E_{s}L + V_{g} - V_{p}}$$

(11)

SQO, 6(3), 2003

$K_d$  is the domain parameter [9],  $E_s$  is the longitudinal electric field for which the electrons reach their limit speed.

The total intrinsic charge  $Q_{gs}$  on saturation is:

$$Q_{gs} = Q_{g0s} + Q_{g1s} \tag{12}$$

However, the extrinsic zone in the source direction remains unchanged with that of the linear mode, while the second zone in the drain direction becomes the sum of circular and rectangular triangle parts (Fig. 2b) [2,3]. From which we deduce the  $Q_{ss}$  and  $Q_{ds}$  capacities that are stored on these parts:

$$Q_{ss} = Q_{sl} = qN_d Z \left\{ \frac{\pi}{2} \frac{d_{0s}^2}{2} \right\}$$

(13)

$$Q_{ds} = qN_d Z \left\{ \frac{d_{1s} \sqrt{d_{2s}^2 - d_{1s}^2}}{2} + \frac{d_{2s}^2}{2} \sin^{-1} \left(\frac{d_{1s}}{d_{2s}}\right) \right\} (14)$$

with

$$d_{2s} = a \sqrt{\frac{V_{bi} + V_d + V_g}{V_p}}$$

.

The total charge  $Q_{gps}$  due to these extensions in the saturation mode is then:

$$Q_{gps} = qN_dZ \times$$

$$\times \left\{ \frac{\pi}{2} \frac{{d_{0s}}^2}{2} + \frac{{d_{1s}} \sqrt{{d_{2s}}^2 - {d_{1s}}^2}}{2} + \frac{{d_{2s}}^2}{2} \sin^{-1} \left( \frac{{d_{1s}}}{{d_{2s}}} \right) \right\}. (15)$$

Finally, the total charge of the gate  $Q_s$  in the saturation mode is equal to:

$$\begin{aligned} Q_{s} = &qN_{d}Z \left\{ \left( \frac{(L - L_{s})}{2} (d_{0s} + d_{1s}) \right) + Lsd_{1s} + \right. \\ &\left. + \left( \frac{\pi}{2} \frac{d_{0s}^{2}}{2} + \frac{d_{1s} \sqrt{d_{2s}^{2} - d_{1s}^{2}}}{2} + \frac{d_{2s}^{2}}{2} \sin^{-1} \left( \frac{d_{1s}}{d_{2s}} \right) \right\} . (16) \end{aligned}$$

#### 3. Capacities determination

We will determine the analytical expressions of these capacities in the linear and saturation regimes of the transistor.

#### 3.1. The gate-source capacity

#### 3.1.1. Linear regime

The gate-source capacity in the linear regime, noted  $C_{gs}$  is given by:

Here:

$$\frac{\partial Q_{gl}}{\partial V_g}\bigg|_{V_d} = C_{gsl}$$

- the intrinsic capacity (17a)

$$\frac{\partial Q_{gl}}{\partial V_g}\bigg|_{V_d} = C_{gspl}$$

- the parasitic capacity (17b)

After we find the following equations:

$$C_{gsl} = \frac{\partial Q_{gl}}{\partial V_g} \bigg|_{V_d} = qN_d ZL \frac{a^2}{4V_p} \left\{ \frac{1}{d_{0l}} + \frac{1}{d_{1l}} \right\}$$

(18)

$$C_{gspl} = qN_d Z \frac{\pi}{2} \frac{a^2}{V_p} \tag{19}$$

$$C_{gs} = qN_d Z \left\{ \frac{L_a^2}{4V_p} \left( \frac{1}{d_{0l}} + \frac{1}{d_{1l}} \right) + \frac{\pi}{2} \frac{a^2}{V_p} \right\}$$

(20)

## 3.1.2. Saturation regime

In this mode, the gate-source capacity noted  $C'_{gs}$  is then equal to:

$$C'_{gs} = \frac{\partial Q_s}{\partial V_g} \bigg|_{V_d} = \frac{\partial Q_{gs}}{\partial V_g} \bigg|_{V_d} + \frac{\partial Q_{gps}}{\partial V_g} \bigg|_{V_d}$$

(21)

Here:

$$\frac{\partial Q_{gs}}{\partial V_g}\bigg|_{V_d} = C_{gss}$$

- the intrinsic capacity (21a)

$$\frac{\partial Q_{gps}}{\partial V_g}\Big|_{V_J} = C_{gsps}$$

- the parasitic capacity (21b)

After we find the following expressions:

$$\begin{split} C_{gss} &= qN_d Z \left\{ \frac{a^2}{4V_p} \left[ \frac{L - L_s}{d_{0s}} + \frac{L + L_s}{d_{1s}} \left( 1 + \left( \frac{V_c}{V_g - V_t} \right)^2 \right) \right] + \\ &+ \frac{K_d \left( d_{0s} - d_{1s} \right)}{2E_s \sqrt{1 + b^2}} \left( \frac{V_c}{V_g - V_t} \right)^2 \right\}. \end{split}$$

406 SQO, 6(3), 2003

$$C_{gsps} = qN_d Z \frac{a^2}{4V_p} \left\{ \pi + 2\sqrt{\frac{{d_{2s}}^2 - {d_{1s}}^2}{{d_{1s}}^2}} + 2\sin^{-1}\left(\frac{d_{1s}}{d_{2s}}\right) + \right.$$

$$+2\sqrt{\frac{{d_{2s}}^2 - {d_{1s}}^2}{{d_{1s}}^2}} \left(\frac{V_c}{V_g - V_t}\right)^2$$

(22)

$$C'_{gs} = qN_d Z \left\{ \frac{a^2}{4V_p} \left[ \pi + \frac{L - L_s}{d_{0s}} + 2\sin\left(\frac{d_{1s}}{d_{2s}}\right) + \right] \right\}$$

$$+\left(\frac{L_{s}+L}{d_{1s}}+2\sqrt{\frac{d_{2s}^{2}-d_{1s}^{2}}{d_{1s}^{2}}}\right)\left(1+\left(\frac{V_{c}}{V_{g}-V_{t}}\right)^{2}\right)\right]+\tag{23}$$

$$+\frac{K_d (d_{0s} - d_{1s})}{2E_s \sqrt{1 + b^2}}$$

(24)

$$b = \frac{\pi K_d \left( V_d - V_c \right)}{2aE_s} \tag{25}$$

# 3.2. The gate-drain capacity

We follow the same steps as previously.

# 3.2.1. Linear regime

The gate-drain capacity on the linear regime, noted  $C_{gd}$ , is calculated as follows:

$$C_{gd} = \frac{\partial Q_l}{\partial V_d} \bigg|_{V_a} = \frac{\partial Q_{gl}}{\partial V_d} \bigg|_{V_a} + \frac{\partial Q_{gpl}}{\partial V_d} \bigg|_{V_a}$$

(26)

With:

$$\frac{\partial Q_{gl}}{\partial V_d}\bigg|_{V_o} = C_{gdl}$$

- the intrinsic capacity (26a)

$$\frac{\partial Q_{gpl}}{\partial V_d}\bigg|_{V_a} = C_{dgpl}$$

– the parasitic capacity (26b)

Then we find:

$$C_{gdl} = qN_d ZL \frac{a^2}{4V_p} \frac{1}{d_{ll}}$$

(27)

$$C_{gdpl} = qN_d Z \frac{\pi}{4} \frac{a^2}{V_p} \tag{28}$$

$$C_{gd} = qN_d Z \frac{a^2}{4Vp} \left\{ \frac{L}{d_{1l}} + \pi \right\}$$

(29)

# 3.2.2. Saturation regime

Similarly, the gate-drain capacity in the saturation regime, noted  $C'_{gd}$ , is equal to:

$$C'_{gd} = \frac{\partial Q_s}{\partial V_d} \bigg|_{V_g} = \frac{\partial Q_{gs}}{\partial V_d} \bigg|_{V_g} + \frac{\partial Q_{gps}}{\partial V_d} \bigg|_{V_g}$$

(30)

Here

$$\frac{\partial Q_{gs}}{\partial V_d}\bigg|_{V_g} = C_{gds}$$

- the intrinsic capacity (30a)

$$\frac{\partial Q_{gps}}{\partial V_d}\bigg|_{V_g} = C_{gdps}$$

- the parasitic capacity (30b)

After various calculations, we arrive to the following expressions:

$$C_{gds} = qN_d Z \frac{K_d (d_{1s} - d_{0s})}{2E_s \sqrt{1 + b^2}}$$

(31)

$$C_{gdps} = qN_d Z \frac{a^2}{2V_p} \sin^{-1} \left( \frac{d_{1s}}{d_{2s}} \right)$$

(32)

$$C_{gd}, \qquad C'_{gd} = qN_d Z \left\{ \left( \frac{K_d (d_{1s} - d_{0s})}{2E_s \sqrt{1 + b^2}} \right) + \left( \frac{a^2}{2V_p} \sin^{-1} \left( \frac{d_{1s}}{d_{2s}} \right) \right) \right\}$$

(26)

#### 4. Results and discussion

On the basis of the previous analytical expressions, the variation of capacities with the bias was carried out for the transistor MESFET1[3], whose parameters are given in the Table 1.

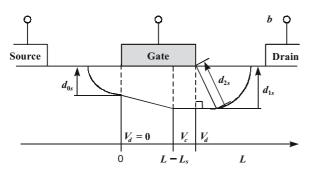

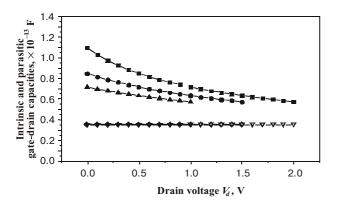

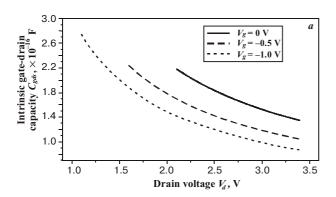

On Fig. 3 show the variation of two components of the gate-drain capacity, the intrinsic component  $C_{gdl}$  and the parasitic component  $C_{gdpl}$  in the linear mode, according to the drain voltage, for various values of the gate voltage.

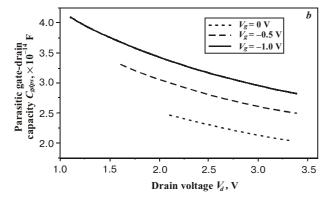

On Fig. 4, we present the intrinsic capacity  $C_{gds}$  (Fig. 4a) and the parasitic capacity  $C_{gdps}$  (Fig. 4b) in the saturation mode. We see that the  $C_{gds}$  capacity always varies at the same rhythm in the linear mode, whereas the  $C_{gdps}$  capacity increases with the drain voltage and decreases with the gate voltage. We note also that the parasitic capacity is about hundred times the intrinsic capacity, it is the capacity which dominates in the saturation mode.

SQO, 6(3), 2003 407

Table 1. MESFET1 parameters.

| TRANS.  | L, µm | a, μm | z, µm | $V_{bi}$ , $\mu$ m | $\mu_0$ , m <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | $v_s$ , ms <sup>-1</sup> | $N_d$ , m <sup>-3</sup> |

|---------|-------|-------|-------|--------------------|----------------------------------------------------------|--------------------------|-------------------------|

| MESFET1 | 1     | 0.2   | 200   | 0.75               | 0.3                                                      | $1.0 \ 10^5$             | $1.0 \ 10^{23}$         |

Fig. 3. Intrinsic and parasitic gate-drain Capacities on the linear regime.

Fig. 4. a – intrinsic gate-drain capacity on the saturation regime; b – parasitic gate-drain capacity on the saturation regime.

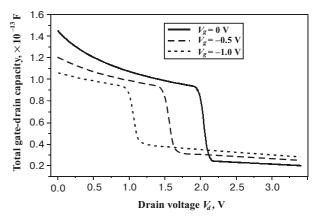

On Fig. 5, we present the total gate-drain capacity in the two modes of polarisation. As we have seen previously, this capacity decreases slightly with the drain tension in the linear mode, whereas it is almost invariant in the saturation mode. We note also the discontinuous transition between the two modes of polarisation and an overlapping between the characteristics.

Fig. 5. Total gate-drain capacity.

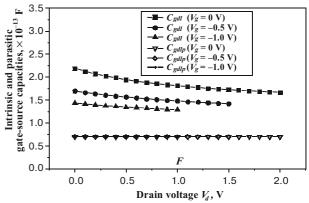

On Fig. 6, we illustrate the intrinsic component  $C_{gsl}$  and the parasitic component  $C_{gspl}$  of the gate-source capacity according to the biasing drain, for different values of the gate voltage in the linear regime. We note that the  $C_{gsl}$  capacity decreases slightly with the drain voltage, and that decrease increases with the gate voltage. Also, and for a fixed value of the drain voltage, this capacity decreases with the gate voltage. However, the  $C_{gspl}$  capacity is invariant. In addition, the intrinsic capacity is increasingly higher than the parasitic capacity in this mode of polarisation.

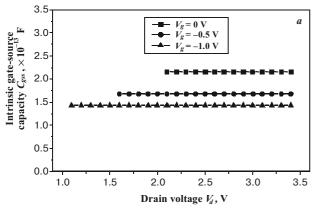

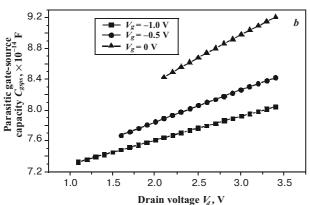

In the saturation mode, we observe (Fig. 7a) that the intrinsic gate-source capacity  $C_{gss}$  becomes invariant towards the drain voltage, and always increases with the gate voltage. Contrary to the gate-drain capacity, this capacity always maintains its order of magnitude. However, the parasitic gate-source capacity  $C_{gsps}$  (Fig. 7b) increases constantly with the drain voltage, and increases with the gate voltage.

Fig. 6. Intrinsic and parasitic gate-source capacities on the linear regime.

408 SQO, 6(3), 2003

Fig. 7. a – intrinsic gate-source capacity on the saturation regime; b – parasitic gate-source capacity on the saturation regime.

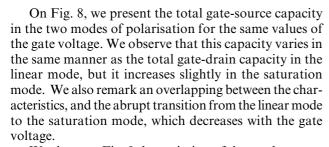

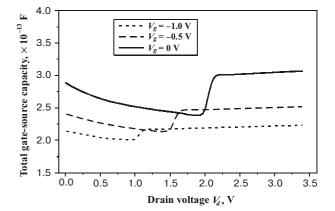

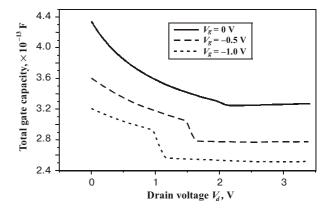

We show on Fig. 9 the variation of the total gate capacity, which is the sum of the total gate-drain and gate-source capacities. The first remark that we raise is the disappearance of the overlapping between the characteristics, like it have been seen for the total capacities. Secondly, we note that the abrupt transition between the linear mode and the saturation mode becomes increasingly weak as the gate voltage augment.

Table 2. Parameters of the transistors used.

Fig. 8. Total gate – source capacity.

Fig. 9. Total gate capacity.

To validate results obtained with our model, we compare them with the experimental measurements taken from the literature for several transistors Table 2.

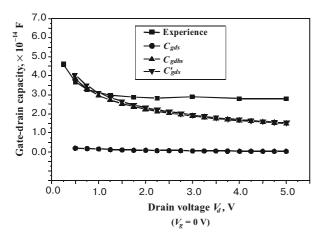

On Fig. 10, we present the experimental characteristics of the gate-drain capacity of the MESFET3 [11], versus the drain voltage at  $V_g = 0$  V. We also plot the curves of the intrinsic capacity  $C_{gds}$ , the parasitic capacity  $C_{gdps}$  and their sum  $C'_{gds}$ . We remark that the curve of the  $C'_{gds}$  capacity has the same behaviour towards the drain voltage as the experimental curve.

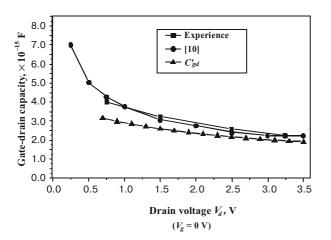

On Fig. 11, we present the experimental gate-drain capacity versus the drain voltage at  $V_g = 0$  V for the transistor MESFET2 [10]. We also present the theoretical results [10]. For our model, we present the gate-drain capacity  $C'_{gd}$ . We can note a good agreement with the experimental results.

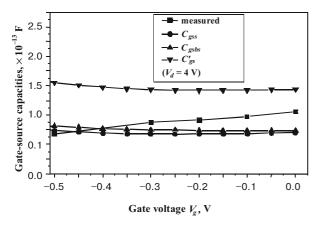

On Fig. 12, we present the experimental gate-source capacity versus the gate voltage, at  $V_d = 4$  V, for the

| TRANS.  | a, µm                 | Z, µm | L, µm | $\mu_0$ , m <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | $v_s$ , ms <sup>-1</sup> | $E_s$ , V·m <sup>-1</sup> | $V_p, V$ | $V_t, V$         | $N_d$ , cm <sup>-3</sup> |

|---------|-----------------------|-------|-------|----------------------------------------------------------|--------------------------|---------------------------|----------|------------------|--------------------------|

| MESFET2 | $167 \\ 10^{-3}$      | 150   | 0.5   | $\frac{23}{10^{-2}}$                                     | 1.96<br>10 <sup>5</sup>  | 8.5<br>10 <sup>5</sup>    | 1.4      | $-65 \\ 10^{-2}$ | $72 \\ 10^{21}$          |

| MESFET3 | 7<br>10 <sup>-2</sup> | 35    | 0.5   | 33<br>10 <sup>-2</sup>                                   | 10 <sup>5</sup>          | 33<br>10 <sup>3</sup>     | 1.75     | -1               | 5<br>10 <sup>23</sup>    |

SOO, 6(3), 2003 409

Fig. 10. Compared theoretical and experimental results for MESFET 2.

Fig. 11. Compared theoretical and experimental results for MESFET 3.

Fig. 12. Compared theoretical and experimental results for MESFET 3.

MESFET3 [11]. We also present the intrinsic capacity  $C_{gss}$ , the parasitic capacity  $C_{gsps}$  and their sum  $C'_{gs}$ .

#### 5. Conclusions

A new accurate expression for simulating the bias dependencies of the GaAs MESFET junction capacities has been presented in this work. The proposed capacities model is very suitable and useful as a means of describing the C(V) characteristics of the GaAs MESFET. Experimental results show excellent agreement with our results.

# References

- C.J. Rodriguez- tellz, K. Mezhzr, and M. AL-Daas, Improved junction capacitance model for the GaAs MESFET // IEEE Trans. On Elect. Devices, 40, (1993).

- T.H. Chen, M.S. Shur, A capacitance model for GaAS MESFET's // IEEE Trans. On Elect. Devices, 32, p. 5 (1985).

- 3. M. Nawaz, T.A. Feldly, A new charge conserving capacitance model for GaAs MESFET's // IEEE Trans. On Elect. Devices, 44, p. 11 (1997).

- T. Takda, K. Yokoyama, M. Ida, T. Sudo, A MESFET variable capacitance model for GaAs integrated circuits simulation // IEEE Trans. On M. T. T., 30, pp. 719-723 (1982).

- 5. M.S. Shur, GaAs devices and circuits, New York: Plenum (1987).

- T.A. Fjeldly, A. Paulsen, F. Tensen, A GaAs MESFET small signal equivalent circuit including transmission line effects // IEEE Trans. On Elect. Devices, 36, pp. 1557-1563 (1989).

- 7. K. Lee, M.S. Shur, T.A. Fjeldly, T. Ytterdal, Semi-conductor devices modeling for VLSI // in series in electronices and VLSI, New Jersy: Prentice-hall (1993).

- 8. S. D'Agostino, G. D'Inzeo, P. Marietti, Analytic physics-based expressions for the empirical parameters of the Staz Pucel MESFET model // IEEE Trans. On M. T. T., 40(7) pp. 1576-1581, (1992).

- 9. M.S. Shur, Analytical models of GaAs FET's // IEEE Trans. On Elect. Devices, 32, p. 1 (1985).

- S. D'Agostino, A.B. Berutto, Physics based Expressions for non-linear Capacitance of the MESFET equivalent circuitd // IEEE Trans. On M.T.T., 42(3), pp. 403-406, (1994).

- 11. S. Akhtar, S. Tiwari, Non quasistatic transient and small signal two dimensional modelling of GaAs MESFET's with emphasis on distributed effects // IEEE Trans. On Elect. Devices, 40, pp. 2154-2163 (1993).

410 SOO, 6(3), 2003